# Uncertainty Quantification for Robust Topology Optimization of Power Transistor Devices

Piotr Putek<sup>1,2</sup>, Peter Meuris<sup>3</sup>, Roland Pulch<sup>2</sup>, Jan ter Maten<sup>1</sup>, Wim Schoenmaker<sup>3</sup> and Michael Günther<sup>1</sup>

<sup>1</sup>Chair of Applied Mathematics and Numerical Analysis, Bergische Universität Wuppertal,

D-42119 Wuppertal, Germany, {putek, termaten, guenther}@math.uni-wuppertal.de

<sup>2</sup> Institute for Mathematics and Computer Science, Ernst-Moritz-Arndt-Universität Greifswald,

D-17487 Greifswald, Germany, pulchr@uni-greifswald.de

<sup>3</sup>MAGWEL NV, B-3000 Leuven, Belgium, {Peter.Meuris,Wim.Schoenmaker}@magwel.com

In this paper we focus on incorporating a stochastic collocation method (SCM) into a topology optimization for a power semiconductor device with both material and geometrical uncertainties. Such geometrical and material variations, which result predominantly from lithography proximity and process imperfections, have a direct impact on its yield and performance. This results in a stochastic direct problem and in consequence, affects the formulation of an optimization problem. Specifically, we deal with the robust optimization of a power transistor in order to minimize the current density overshoots, since the change of the shape and topology of a device layout is the proven technique for the reduction of a hotspot area. The gradient of a cost functional is evaluated using the sensitivity equation and the adjoint variable method. In simulations, we apply the level set method with a distribution additionally modified by the topological derivative, for the representation of the interface. Finally, we show the results of the robust optimization for the power transistor device, which is an example of a relevant problem in nanoelectronics, and also used widely in the automotive industry.

Index Terms-uncertainty quantification (UQ), robustness, topology, design optimization, nanoelectronics, power transistors.

# I. INTRODUCTION

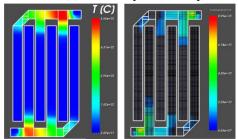

THE POWER semiconductor devices play a key role in L efficiently exploiting resources and energy in power electronics with respect to both an energy harvesting and distribution as well as in applications for automotive industry. In fact, due to the proximity effect in lithography and several process variations, the physical domain of power devices made of several thousands of parallel channel devices, cannot be determined precisely. In particular, the imperfections in manufacturing processes related primarily to sub-wavelength lithography, lens aberration, and chemical-mechanical polishing belong to the most important variation issues, since they directly influence both the yield and performance [9]. In consequence, they determine also the acceptability, reliability and profitability of power electronic systems, which depend mainly on variation tolerances, e.g., [5]. This, in turn, is especially important in automotive applications that require the handling of electro-thermal operational constraints to the design of both components and systems. In this context, the localized imperfections of the die inside may result in the formation of a 'hot spot' (see Fig.4) that rapidly heats and leads to the destruction of a power device, e.g., [1, 7].

The problem of a thermal instability has been known to the automotive industry since the year 1997 when the very fast switching MOSFET devices were introduced onto the market [7]. This phenomenon, which is a main reason for the reduction of the safe operating area, results from a temperature instability mechanism induced by an uneven distribution in drain current as a side effect of the progressive die size and the process scaling down [1]. However, the positive temperature coefficient in a wide range of drain currents, which causes a kind of second breakdown phenomenon, is related to the geometrical and physical parameters of a power device [1, 2].

From this point of view, it is possible to reduce a thermal instability by optimizing the geometry within the device layout while taking both the conductive power losses and robustness into account. Therefore, in this work we apply the SCM [8] with the Polynomial Chaos (PC) for the assessment of the reliability and robustness of a design w.r.t. uncertain parameters from manufacturability, e.g., tolerances variations, described by random variables. This solution allows for the efficient calculation of statistical moments and additionally yields directly a response surface model, which can be easily incorporated in a robust topology optimization, e.g., [6].

A novelty of this paper is to incorporate the SCM into the Level Set Method (LSM) in order to eliminate hot-spot phenomena while taking the geometrical and material variations into account. The latter is an important requirement in real engineering applications where designers ought to consider some manufacture tolerances during the optimization process.

Fig. 1. Structure in a power transistor device [3].

## II. STOCHASTIC FORWARD PROBLEM

The special construction of a power device, shown in Fig. 1, is considered here as a case study. The source and drain contacts are placed on the top of the design. It consists of several thousands of parallel channel devices, where the current to drain and away from the sources of the individual channel is transported by complex series of metal stripes and via patterns. For the UQ analysis, we substitute some parameters  $\boldsymbol{\xi}$  in a model (1) by independent random variables defined on some probabilistic space. Then, the current-flow pattern can be described by the coupled, random-dependent PDEs on  $\Omega \subset \mathbf{R}^3$

$$\left\{ \begin{array}{l} \nabla \cdot \left( \varepsilon \mathbf{E} \right) = \rho, \\ \nabla \cdot \mathbf{J}_{(n/p)} \stackrel{\mp}{=} q \partial_{i} \left( n / p \right) \stackrel{\mp}{=} q R \left( p, n \right) = \mathbf{0}, \\ \mathbf{J}_{(n/p)} = q \cdot \left( n / p \right) \cdot \mu_{(n/p)} \mathbf{E} \pm q D_{(n/p)} \nabla \left( n / p \right), \\ C_{\nu} \partial_{i} T = \nabla \cdot \lambda \left( T \right) \nabla T + \sigma \left\| \mathbf{E} \right\|^{2}, \end{array} \right.$$

$$(1)$$

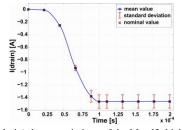

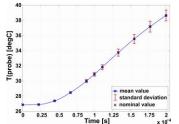

endowed with suitable boundary and initials conditions. Here,  $\rho$ ,  $\varepsilon$  and q denote the charge density, the permittivity and the elementary charge, respectively.  $\mathbf{E}(\mathbf{x}, t, \boldsymbol{\zeta})$  is the electric field. The concentration of holes and electrons is represented by n and p, while (n/p) describes compactly equations for electrons and holes.  $D_{(n/p)}$ ,  $\mu_{(n/p)}$ ,  $\mathbf{J}_{(n/p)}(\mathbf{x}, t, \boldsymbol{\zeta})$  are the diffusion, mobility and current densities of electrons and holes.  $T(\mathbf{x}, t, \boldsymbol{\zeta})$ ,  $C_v$  and  $\lambda(T)$  denote the temperature, the heat capacitance and the thermal conductivity. The conductivity of k-th layer is defined as  $\sigma = W_k \sigma_k$ , where  $\sigma_k = f(q, n, p, \mu_{(n/p)})$  and  $W_k$  is the layer size. The basic idea of using the SCM for the solution of a time-dependent random process (1) is to provide the solution of a deterministic problem at collocation points  $\boldsymbol{\zeta}^{(k)}$ , k = 0, ..., K. This, in turn, also yields an approximation of statistical moments using the PC expansion [8], shown on Fig. 2 and 3.

Fig. 2. UQ of I(drain) due to variations of the Metal3 thickness, modeled by a Gaussian distribution with 10% variation around a mean  $1\mu m$ .

Fig. 3. UQ of T(probe) due to variations of the  $\sigma$  of the Metal3, modeled by a uniform distribution with 15% variation around a mean 20 MS/m.

#### **III. STOCHASTIC OPTIMIZATION PROBLEM**

The problem of the shape optimization of the device layout corresponds to the minimization of a converted cost functional using the weighted aggregation method [4] in a mean sense  $\mathbb{Q}$

$$\min \mathbb{Q}\left[F\right] = w_{1}\mathbb{Q}\left[I^{-1}\int_{T}\int_{\Omega}\mathbf{E}\left(\phi,\boldsymbol{\xi}\right)dxdt\right] +$$

$$w_{2}\mathbb{Q}\left[\sigma^{-1}\left(\phi,\boldsymbol{\xi}\right)\int_{T}\int_{\Omega}\left|\mathbf{J}\left(\phi,\boldsymbol{\xi}\right)\right|^{2}dxdt\right] + \beta\int_{\Gamma}\left|\nabla\phi\right|^{2}dx$$

(2)

where  $\phi$  is a signed distance function. The fidelity term consists of two terms related to the output impedance and the dissipated electrical power. The Tikhonov regularization (last term) penalizes the oscillation of level sets with a smoothing effect, controlled by  $\beta$ . A priori information about objective functions is given by the prescribed weights  $w_1$ ,  $w_2$ . To predict the sensitivity for the current source problem a Gâteaux differential can be used. Then, after formulating and solving the dual problem ( $\mathbf{E}^*$ ), it is defined in the level set framework as

$$d_{\phi}F = \delta\left(\phi\right) \left[ w_{1}\left(\sigma_{1} - \sigma_{2}\right) \int_{T} \int_{\Gamma} \mathbf{E} \cdot \mathbf{E}^{*} dx dt + w_{2} \int_{T} \int_{\Gamma} \mathbf{J} \cdot \mathbf{E}^{*} dx dt \right]$$

(3)

with the Dirac function  $\delta(\phi)$  and, e.g.,  $\sigma$  represented by

$$\sigma\left(\phi,\boldsymbol{\xi}\right) = \sigma_{1}\left(\xi_{1}\right)H\left(\phi\right) + \sigma_{2}\left(\xi_{1}\right)\left[1 - H\left(\phi\right)\right] \tag{4}$$

With the smeared-out Heaviside function  $H(\phi)$ . For the voltage sensitivity problem, the Tellegen's theorem can be applied to incorporate results (3) into the optimization problem (2).

Fig. 4. Hot-spot phenomenon in the Metal3 layer for a case study [3]: temperature distribution (left), violations of current density (right).

# ACKNOWLEDGMENT

The project nanoCOPS (Nanoelectronic Coupled Problems Solutions) is supported by the European Union in the FP7-ICT- 2013-11 Program under the grant agreement 619166.

## IV. REFERENCES

- A. Consoli, *et al.*, "Thermal Instability of Low Voltage Power-MOSFET's," *IEEE Trans. on Pow. Electron.*, vol. 15, no. 3, pp. 575-581, May 2000.

- [2] G Greco and S. Rinaudo, "Automatic Layout Optimization of Power Discrete devices using innovative distributed model techniques," *Pro*gress in Industrial Mathematics at ECMI 2010, Mathematics in Industry 17, Springer Berlin Heidelberg, 2012, pp. 77-83.

- [3] Magwel software 6.4, MAGWEL NV, B-3000 Leuven, Belgium.

- [4] T. Maler, A Study of Multi-Objective Optimization Methods: for Engineering Applications, VDM Verlag, 2009.

- [5] S.P. Mohanty, E. Kougianos, "Incorporating Manufacturing Process Variation Awareness in Fast Design Optimization of Nanoscale CMOS VCOs," *IEEE Trans. on Semicond. Manufact.*, vol.27, no.1, pp. 22-31, Feb. 2014.

- [6] P. Putek, et al., "Robust topology optimization of a Permanent Magnet synchronous machine using level set and stochastic collocation methods," accepted for Progress in Industrial Mathematics at SCEE 2014, Mathematics in Industry, Springer (2015).

- [7] J.L. Shue and H.W. Leidecker, "Power MOSFET Thermal Instability operation characterization support," report NASA/TM-2010-216684, pp. 1-15, Apr. 2010.

- [8] D. Xiu, "Efficient collocational approach for parametric uncertainty analysis," *Commun. Comput. Phys.*, vol. 2, no. 2, pp. 293-309, Apr. 2007.

- [9] Y. Ban, and D.Z. Pan, "Modeling of Layout Aware Line-Edge Roughness and Poly Optimization for Leakage Minimization," *IEEE Journal* on Emerg. and Select. Topics in Circuits and Systems, vol.1, no.2, pp. 150-159, June 2011.